74HC595¶

Der 74HC595 besteht aus einem 8-Bit-Schieberegister und einem Speicherregister mit dreizuständigen parallelen Ausgängen. Er wandelt serielle Eingaben in parallele Ausgaben um, sodass IO-Ports eines MCU gespart werden können.

Bei hohem Pegel an MR (Pin10) und niedrigem Pegel an OE (Pin13) wird die Daten am steigenden Flanken von SHcp eingelesen und durchlaufen das Speicherregister über die steigende Flanke von SHcp.

Wenn die beiden Taktgeber miteinander verbunden sind, liegt das Schieberegister immer einen Taktimpuls vor dem Speicherregister.

Im Speicherregister gibt es einen seriellen Schiebeeingangspin (Ds), einen seriellen Ausgangspin (Q) und eine asynchrone Reset-Taste (niedriger Pegel).

Das Speicherregister gibt einen Bus mit parallelem 8-Bit und in drei Zuständen aus.

Ist OE aktiviert (niedriger Pegel), werden die Daten im Speicherregister zum Bus (Q0 ~ Q7) ausgegeben.

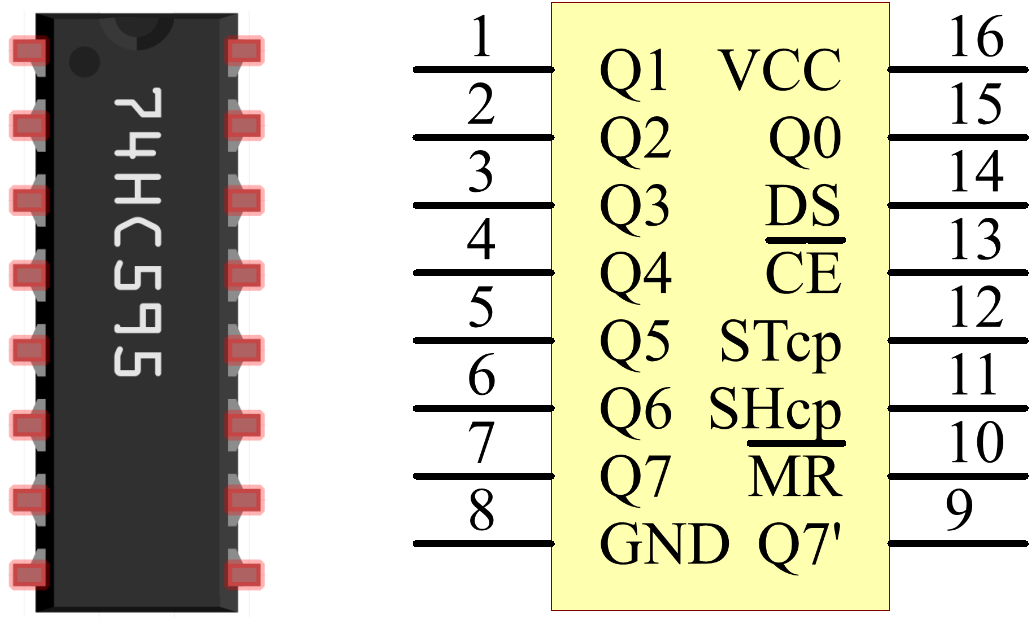

Pins des 74HC595 und ihre Funktionen:

Q0-Q7: 8-Bit-parallele Daten-Ausgangspins, direkt für die Steuerung von 8 LEDs oder 8 Pins einer 7-Segment-Anzeige geeignet.

Q7‘: Serieller Ausgangspin, verbunden mit DS eines weiteren 74HC595 zur seriellen Verknüpfung mehrerer 74HC595.

MR: Reset-Pin, aktiv bei niedrigem Pegel.

SHcp: Zeitsequenz-Eingang des Schieberegisters. An der steigenden Flanke rückt die Daten im Schieberegister jeweils um ein Bit vor, d.h. Daten in Q1 bewegen sich zu Q2 usw. An der fallenden Flanke bleiben die Daten unverändert.

STcp: Zeitsequenz-Eingang des Speicherregisters. An der steigenden Flanke wandern die Daten aus dem Schieberegister ins Speicherregister.

OE: Enable-Pin für den Ausgang, aktiv bei niedrigem Pegel.

DS: Serieller Dateneingangspin.

VCC: Positive Versorgungsspannung.

GND: Masse.

Beispiel

5.1 Mikrochip - 74HC595 (Für MicroPython-Anwender)

5.2 Nummernanzeige (Für MicroPython-Anwender)

5.3 Zeitmesser (Für MicroPython-Anwender)

5.4 8x8 Pixel-Grafik (Für MicroPython-Anwender)

7.4 Personen Zähler (Für MicroPython-Anwender)

7.5 SPIEL - 10 Sekunden (Für MicroPython-Anwender)

7.6 Ampel (Für MicroPython-Anwender)

7.12 Digitaler Wasserwaage (Für MicroPython-Anwender)

5.1 Mikrochip - 74HC595 (Für Arduino-Anwender)

5.2 - Zahlenanzeige (Für Arduino-Anwender)

5.3 - Zeitmesser (Für Arduino-Anwender)

5.4 - 8x8 Pixelgrafik (Für Arduino-Anwender)